### R8A66173SP 4-CH 12-BIT PWM GENERATOR

REJ03F0264-0100 Rev.1.00 Jan.24.2008

### **DESCRIPTION**

R8A66173 has four 12-bit PWM (Pulse Width Modulation) circuits which are built by using the CMOS process.

This IC controls PWM waveform by adjusting the "H" width according to serial data sent from MCU (Micro Controller Unit) or other device. Each channel can be independently controlled.

High-resolution digital-analog (D-A) converter can be formed easily by connecting a low-pass filter (LPF) circuit to the output pins of this circuit.

R8A66173 is the succession product of M66242.

### **FEATURES**

- Built-in four 12-bit high-resolution PWM circuits

- Easy D-A conversion Quick output waveform smoothing Control by 1.22mV possible per step (Vcc=5V range)

- Serial data input

- •"H" level width setting type

- 4 channels controlled independently

- All 4 channels reset by reset input (R), High-impedance status after reset

- All 4 channels controlled by output control input (OC)

- Settings take effect after ongoing cycle is completed

- Output : CMOS 3-state output

- Output current lo=±4mA (Vcc=5.0V range), lo=±2mA (Vcc=3.3V range)

- Wide operating supply voltage range (Vcc=3.0~3.6V or Vcc=4.5~5.5V, single power supply)

- Wide operating temperature range: Ta=-40°C~+85°C

#### **APPLICATION**

- Analog signal control in televisions and audio systems

- Control of lamps, heaters and motors

- For software servo in home appliances and industrial machinery

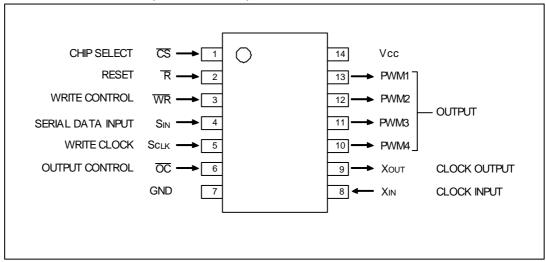

# PIN CONFIGURATION (TOP VIEW)

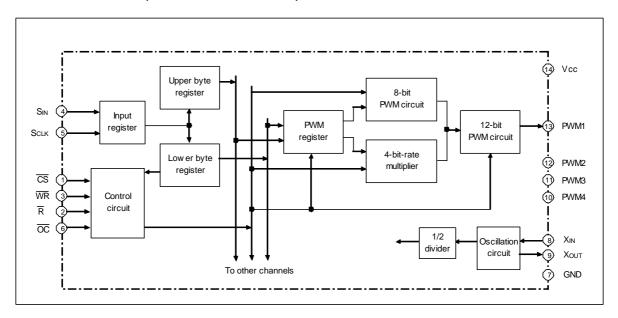

# **BLOCK DIAGRAM (EACH CHANNEL)**

#### **FUNCTION**

The PWM output waveform of each channel is controlled by taking in PWM data from MCU or other device via serial data input SIN.

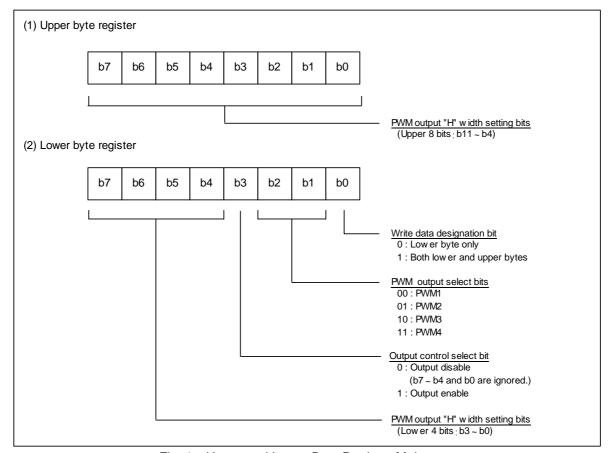

12-bit PWM data is input being divided between upper 8-bits (upper byte) and lower 4-bits.

The lower 4-bit data is combined with command data such as channel designation and input as 8-bit data (lower byte).

The lower byte should be written first, and then the upper byte. Even if only the upper byte is to be changed, rewrite from the lower byte.

The PWM waveform changes according to the new setting from the next cycle.

One cycle of PWM waveform (=4096 divisions; 12-bit resolution) are divided into 16 ( $2^4$ ) subsections t. Each subsection consists of 256 (= $2^8$ ; 8-bit resolution) minimum bits  $\tau$ (=2/fxiN\*\*).

One subsection t consists of an 8-bit PWM waveform (basic waveform). The "H" width of this waveform is determined according to the upper 8-bits of PWM data. One cycle has 16 subsections t, each of which has this basic waveform. Among them, those which are designated by the 4-bit-rate multiplier are conditioned to have a "H" width that is longer by  $\tau$ . The lower 4-bits of PWM data are used to specify those subsections (tm). The waveform of other subsections remains unchanged.

The PWM waveform (12-bit resolution) is a combination of two types of waveforms which are different in "H" width, as described above.

When output control input  $\overline{OC}$  is "H", the output of every 4-channel turns high-impedance from the next cycle. When reset input  $\overline{R}$  is "L", the output of every channel turns high-impedance as soon as the ongoing cycle is completed, and PWM data of all channels is reset. If  $\overline{R}$  input is changed from "L" to "H", the next cycle starts, however, the output of the channels remains high-impedance.

To enable output, rewrite input data for each channel.

\*\*)fxin: Clock Xin repeat frequency

# PIN DESCRIPTIONS

| Pin               | Name                  | Input/Output | Functions                                                                                                                                                                                                                                            |  |  |  |

|-------------------|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R                 | Reset input           | Input        | "L" : All 4-channels put in high-impedance state.                                                                                                                                                                                                    |  |  |  |

| <del></del><br>cs | Chip select input     | Input        | "L" : Communication with MCU becomes possible. $\overline{WR}, S_{IN}$ and $S_{CLK}$ put in enable state.                                                                                                                                            |  |  |  |

| <del></del><br>WR | Write control input   | Input        | "L": Serial data written. "L"-to-"H" edge: Written data stored in upper or lower byte register.                                                                                                                                                      |  |  |  |

| SIN               | Serial data input     | Input        | Inputs 8-bit serial data from MCU synchronously with Sclk clock.                                                                                                                                                                                     |  |  |  |

| Sclk              | Write clock input     | Input        | Inputs sync clock pulses for 8-bit serial data writing.                                                                                                                                                                                              |  |  |  |

| <u>oc</u>         | Output control input  | Input        | "H": All 4-channels put in high-impedance state.                                                                                                                                                                                                     |  |  |  |

| PWM1 ~<br>PWM4    | PWM outputs 1 ~ 4     | Output       | Outputs PWM waveform. (CMOS 3-state output)                                                                                                                                                                                                          |  |  |  |

| XIN               | Clock input           | Input        | Input/output signals generated by clock signal generation circuit. Oscillation frequency is determined by connecting ceramic or quartz resonator between XIN and XOUT. The frequency of internal clock (PWM timing clock) signals is the 1/2 divider |  |  |  |

| Хоит              | Clock output Output W |              | of the frequency input from clock input XIN.  When external clock signals are used, connect clock generator to XIN pin and leave XOUT open.                                                                                                          |  |  |  |

Fig. 1 Upper and Lower Byte Register Makeup

Table 1 Mode Selection

| Mode                                |                          |    |    |     |       |       |      | Inp | ut se | rial d | ata |    |       |       |     |    |    |

|-------------------------------------|--------------------------|----|----|-----|-------|-------|------|-----|-------|--------|-----|----|-------|-------|-----|----|----|

| ivioue                              |                          |    |    | Lov | wer b | yte c | lata |     |       |        |     | Up | oer b | yte d | ata |    |    |

| PWM data setting                    | Lower 4-bit data setting | b7 | b6 | b5  | b4    | 1     | b2   | b1  | 0     |        |     |    |       | -     |     |    |    |

| (output enable) 12-bit data setting |                          | b7 | b6 | b5  | b4    | 1     | b2   | b1  | 1     | b7     | b6  | b5 | b4    | b3    | b2  | b1 | b0 |

| Output                              | Output disable           |    |    | Χ   | Χ     | 0     | b2   | b1  | Х     |        |     |    |       | _     |     |    |    |

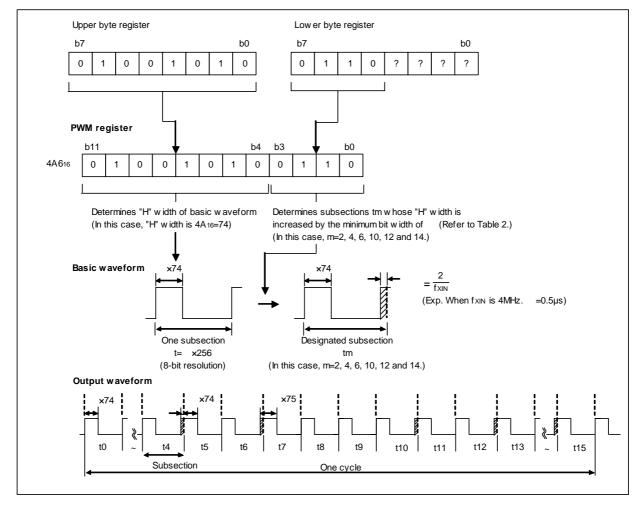

Table 2 Patterns of Lower 4-bits and Subsections whose "H" Width is increased

| PWM register | Subsection tm whose H width is | Number of   |

|--------------|--------------------------------|-------------|

| b3 ~ b0      | increased by $(m = 0 \sim 15)$ | Subsections |

| 0000         | Nothing                        | 0           |

| 0001         | m = 8                          | 1           |

| 0010         | m = 4, 12                      | 2           |

| 0100         | m = 2, 6, 10, 14               | 4           |

| 1000         | m = 1, 3, 5, 7, 9, 11, 13, 15  | 8           |

| 1111         | m = 1 ~ 15 (m 0)               | 15          |

Fig.2 PWM Waveform Output Example (Input data:4A6<sub>16</sub>)

### **OPERATION**

#### Serial Data Input

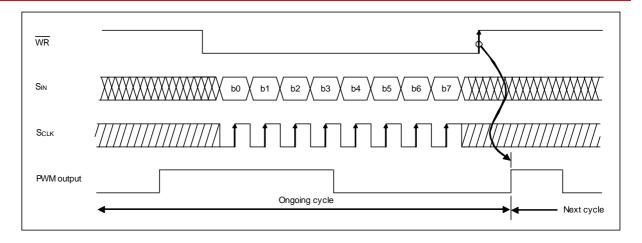

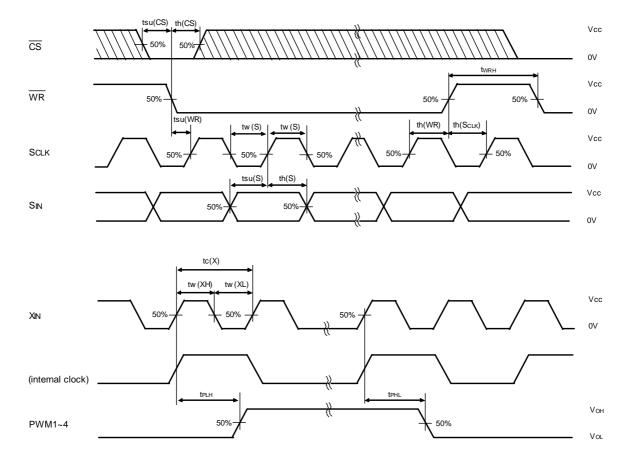

When chip select  $\overline{\text{CS}}$  is "L" and write control input  $\overline{\text{WR}}$  is "L", data input to SIN at the edge where write clock input SCLK status shifts from "L" to "H" is written.(See Fig.3.) At the edge where  $\overline{\text{WR}}$  rises from "L" to "H", the latest 8-bit data writing is completed, and input data is stored in lower (or upper) byte register .When writing on the lower byte or writing on both upper and lower bytes is completed, data on the lower byte register or, in the latter case, data on both lower and upper byte registers is written on the PWM register of the channel designated by lower bytes b2 and b1. All setting process ends with this writing, and PWM waveform changes according to the setting from the next cycle.

### **PWM Waveform Output**

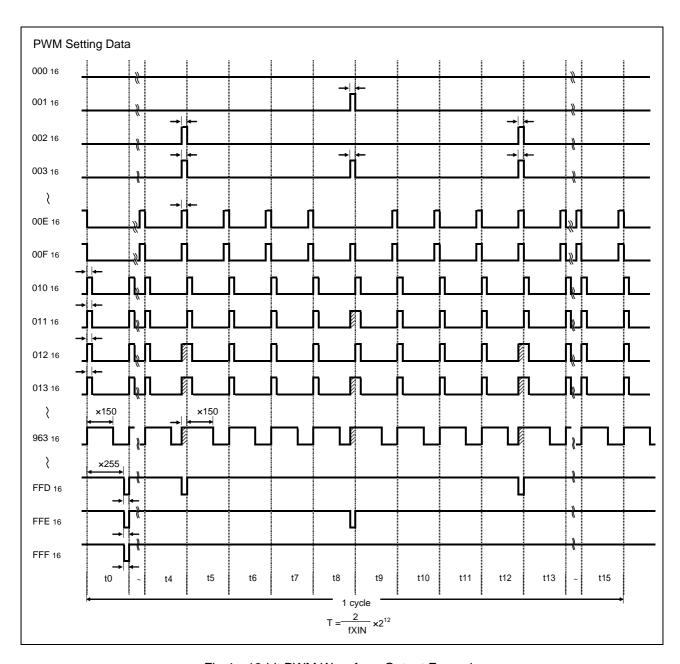

#### (1)12-bit PWM output

One PWM waveform cycle is divided into  $16(=2^4)$  subsections t, and each subsection is further divided into  $256(=2^8)$  minimum resolution bits  $\tau(=2/fxin)$ . The "H" width of subsection t basic waveform is determined by the upper 8-bits of PWM data. (In Fig.2 above, "H" width is  $4A_{16}=74x\tau$ )

Among these 16 subsections t, subsections tm designated by the lower 4-bits of PWM data have "H" width that is longer by  $\tau$ .

(In Fig.2 above, the "H" width of designated 6 subsections (m =2, 4, 6, 10, 12 and 14) is  $4B_{16}=75x_{T}$ .)

The "H" width of undesignated subsections remains unchanged.

As explained above, one cycle of waveform is a combination of two waveforms different in the "H" width.

(In Fig. 2 above, one cycle consists of 10 subsections whose "H" width is  $74x\tau$  and 6 subsections whose "H" width is  $75x\tau$ )

Note: It is impossible to set one whole cycle to "H" level.

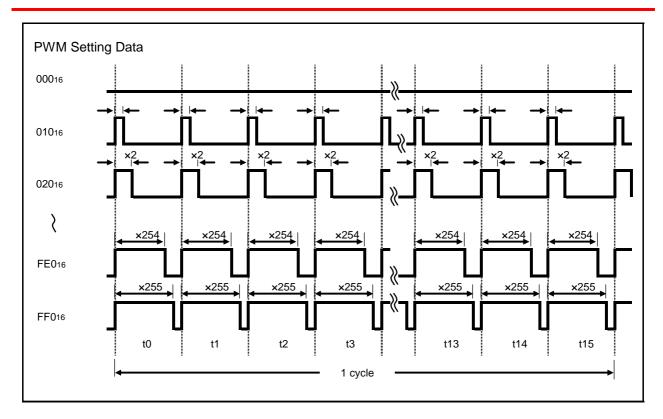

#### (2)8-bit PWM output

As can be seen from the 12-bit PWM waveform output process as described above, 8-bit resolution PWM waveform can be output by fixing the lower 4-bits of PWM data to 00002.

All subsections from t0 to t15 have the "H" width as determined by the upper 8-bits of PWM data.

Note: It is impossible to set one whole cycle to "H" level.

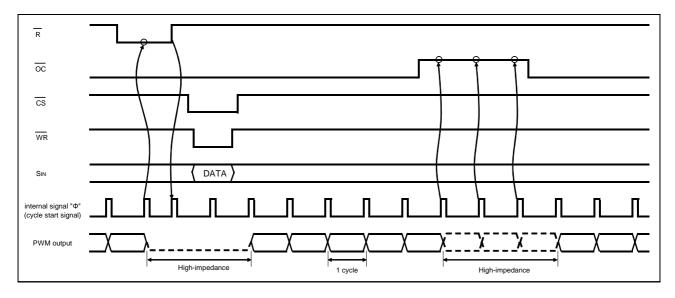

### Output Control

#### (1)Serial data input

By using data on lower byte register b3 (output control selection bit), output of each channel can be controlled independently. The state of the selected PWM output changes after the completion of the ongoing cycle.

When b3 is set 0, lower byte register b0 (write data designation bit) is reset. Do not write on upper byte in this case.

#### (2)Output control input

The status of all 4-channel outputs during a cycle is determined depending on the status of output control input  $\overline{OC}$  at the start of the cycle. (See Fig. 6.)

Even when output is in a high-impedance state, data on each PWM register is retained, and data can be rewritten.

#### (3)Reset

When reset input R turns "L", all operation is reset as soon as the ongoing cycle is completed. The outputs of all 4-channels turn high-impedance. The PWM register of each channel is reset.

When  $\overline{R}$  is shifted from "L" to "H", a next cycle starts, and data writing becomes possible. However, outputs stay in the high-impedance state. (See Fig. 6)

To resume output, write input data for each channel.

#### **Initial State**

After power-on, outputs and PWM register data are unstable.

#### (1)Reset

Reset input  $\overline{R}$  is kept on "L" level for more than one cycle (2.048ms when fxin is 4 MHz) or more, this integrated circuit is put in a reset state.

If stabilization needs more time, e.g. when a quartz resonator is used, keep  $\overline{R}$  on "L" level for an adequate period of time.

#### (2)Serial data input

When starting using this integrated circuit without resetting, input false lower byte data (b0=0) to stabilize lower byte register b0 data, and then input normal data.

Fig.3 Serial Data Write Timing

Fig.4 12-bit PWM Waveform Output Example

Fig.5 8-bit PWM Waveform Output Example

Fig.6 Output Control Timing Chart

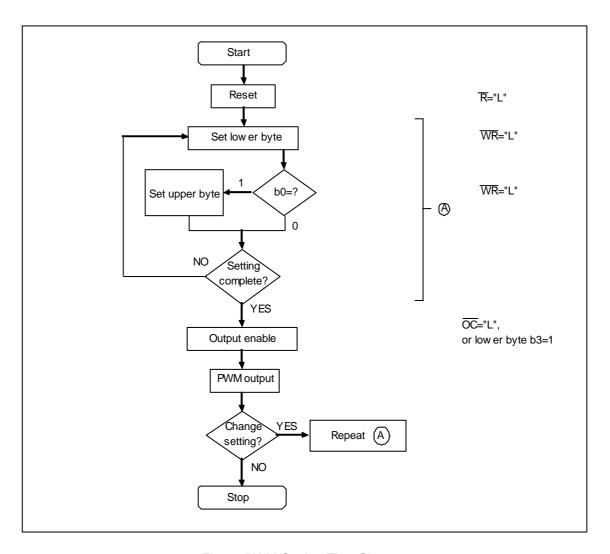

Fig.7 PWM Setting Flow Chart

# ABSOLUTE MAXIMUM RATINGS (Ta= -40°C~85°C unless otherwise noted)

| Symbol | Parameter           | Conditions | Ratings        | Unit |

|--------|---------------------|------------|----------------|------|

| Vcc    | Supply voltage      |            | -0.5 ~ +7.0    | V    |

| Vı     | Input voltage       |            | -0.5 ~ Vcc+0.5 | V    |

| Vo     | Output voltage      |            | -0.5 ~ Vcc+0.5 | V    |

| lo     | Output current      |            | ±15            | mA   |

| Icc    | Supply/GND current  | Vcc, GND   | ±40            | mA   |

| Pd     | Power dissipation   |            | 150            | mW   |

| Tstg   | Storage temperature |            | -65 ~ 150      | °C   |

# RECOMMENDED OPERATING CONDITIONS (Ta=-40 °C ~ 85 °C unless otherwise noted)

| Symbol | Par                   |                             | Limits |      |      |      |  |

|--------|-----------------------|-----------------------------|--------|------|------|------|--|

| Symbol | Fai                   | ameter                      | Min.   | Тур. | Max. | Unit |  |

| Vcc    | Supply voltage        | 5.0V support                | 4.5    | 5.0  | 5.5  | V    |  |

| VCC    | 3.3V support          |                             | 3.0    | 3.3  | 3.6  | V    |  |

| GND    | Supply voltage        | Supply voltage              |        |      |      | V    |  |

| Vı     | Input voltage         | Input voltage               |        |      | Vcc  | V    |  |

| Vo     | Output voltage        | 0                           |        | Vcc  | V    |      |  |

| Topr   | Operating temperature | Operating temperature range |        |      | 85   | °C   |  |

# **ELECTRICAL CHARACTERISTICS**

# ■5.0V version support specifications (Ta=-40 °C ~ 85 °C, Vcc=4.5V ~ 5.5V, unless otherwise noted)

| Symbol | Parameter               |             | Test conditions                       |         | Unit |         |       |

|--------|-------------------------|-------------|---------------------------------------|---------|------|---------|-------|

| Symbol | Faiaille                | itei        | rest conditions                       | Min.    | Тур. | Max.    | Offic |

| VIH    | "H" input voltage       | XIN         |                                       | 0.8Vcc  |      |         | V     |

| VIII   | TT iliput voltage       | Other input |                                       | 0.75Vcc |      |         | V     |

| VIL    | "L" input voltage       | XIN         |                                       |         |      | 0.2Vcc  | V     |

| VIL    | L iliput voltage        | Other input |                                       |         |      | 0.25Vcc | V     |

| Vон    | "H" output voltage      | PWM1~4      | IOH=-4mA                              | Vcc-0.5 |      |         | V     |

| Vol    | "L" output voltage      | PWM1~4      | IoL=4mA                               |         |      | 0.5     | V     |

| lін    | "H" input current       |             | VI=Vcc                                |         |      | 1.0     | μA    |

| lıL    | "L" input current       |             | Vi=GND                                |         |      | -1.0    | μΑ    |

| lozн   | Off-state "H" output cu | rrent       | Vo=Vcc                                |         |      | 5.0     | μΑ    |

| lozL   | Off-state "L" output cu | rrent       | Vo=GND                                |         |      | -5.0    | μA    |

| Icc    | Quiescent supply curr   | ent         | V <sub>I</sub> =Vcc, GND, Output open |         |      | 40      | μΑ    |

# ■3.3V version support specifications (Ta=-40 °C ~ 85 °C, Vcc=3.0V ~ 3.6V, unless otherwise noted)

| Symbol | Parameter               |             | Test conditions                       |         | Limits |         | Unit  |

|--------|-------------------------|-------------|---------------------------------------|---------|--------|---------|-------|

| Symbol | Falaiii                 | etei        | rest conditions                       | Min.    | Тур.   | Max.    | Offic |

| VIH    | "H" input voltage       | XIN         |                                       | 0.8Vcc  |        |         | V     |

| VIII   | Tr input voltage        | Other input |                                       | 0.75Vcc |        |         | V     |

| VIL    | "I " input voltage      | XIN         |                                       |         |        | 0.2Vcc  | V     |

| VIL    | "L" input voltage       | Other input |                                       |         |        | 0.25Vcc | V     |

| Voн    | "H" output voltage      | PWM1~4      | Iон=-2mA                              | Vcc-0.5 |        |         | V     |

| Vol    | "L" output voltage      | PWM1~4      | IoL=2mA                               |         |        | 0.5     | V     |

| Iн     | "H" input current       |             | V <sub>I</sub> =V <sub>C</sub> C      |         |        | 1.0     | μΑ    |

| lıL    | "L" input current       |             | Vi=GND                                |         |        | -1.0    | μA    |

| lozh   | Off-state "H" output of | urrent      | Vo=Vcc                                |         |        | 5.0     | μΑ    |

| lozL   | Off-state "L" output co | urrent      | Vo=GND                                |         |        | -5.0    | μΑ    |

| Icc    | Quiescent supply cur    | rent        | V <sub>I</sub> =Vcc, GND, Output open |         |        | 40      | μΑ    |

# SWITCHING CHARACTERISTICS

(Ta=-40 °C ~ 85 °C, Vcc=5.0V±0.5V or 3.3V±0.3V, unless otherwise noted)

| Svmbol   | Param                   | eter             | Test conditions   | 5.0\ | / specifica | ation | 3.3\ | / specifica | ation | Unit  |

|----------|-------------------------|------------------|-------------------|------|-------------|-------|------|-------------|-------|-------|

| Cyrribor | i aiaiii                | otor             | 1 CSt COTTUILIONS | Min. | Тур.        | Max.  | Min. | Тур.        | Max.  | Offic |

| fmax     | Maximum clock frequency | XIN              | CL=50pF           |      |             | 16    |      |             | 12.5  | MHz   |

| tPLH     | Output "L-H", "H-L"     | XIN-PWM1~4       | (Note 1)          |      |             | 100   |      |             | 100   | ns    |

| tPHL     | propagation time        | XIN-F VVIVI I ~4 |                   |      |             | 100   |      |             | 100   | ns    |

# $\textbf{TIMING REQUIREMENTS} \ (\text{Ta=-40 °C $^{\circ}$C, Vcc=5.0V$\pm0.5V or 3.3V$\pm0.3V, unless otherwise noted})$

| Symbol   | Parameter                               | Test conditions  | 5.0√   | / specifica | ition | 3.3\   | / specifica | ition | Unit  |

|----------|-----------------------------------------|------------------|--------|-------------|-------|--------|-------------|-------|-------|

| Symbol   | raidilletei                             | Test corrantorio | Min.   | Тур.        | Max.  | Min.   | Тур.        | Max.  | Offic |

| tc(X)    | XIN cycle time                          |                  | 62.5   |             |       | 80     |             |       | ns    |

| tw(XH)   | Xเท "H" pulse width                     |                  | 32.5   |             |       | 40     |             |       | ns    |

| tw(XL)   | Xเก "L" pulse width                     |                  | 30     |             |       | 40     |             |       | ns    |

| tw(S)    | Sclk pulse width                        |                  | 30     |             |       | 40     |             |       | ns    |

| twRH     | WR "H" hold time                        |                  | 6tc(x) |             |       | 6tc(x) |             |       | ns    |

| tsu(CS)  | CS "L" setup time before WR↓            |                  | 30     |             |       | 40     |             |       | ns    |

| tsu(WR)  | WR "L" setup time before Sc∟κ           |                  | 30     |             |       | 40     |             |       | ns    |

| tsu(S)   | Sin setup time before Sclk <sup>↑</sup> |                  | 50     |             |       | 60     |             |       | ns    |

| th(CS)   | CS "L" hold time after WR↓              |                  | 30     |             |       | 40     |             |       | ns    |

| th(WR)   | WR "L" hold time after ScLK             |                  | 10     |             |       | 20     |             |       | ns    |

| th(S)    | SIN hold time after SCLK                |                  | 10     |             |       | 20     |             |       | ns    |

| th(SCLK) | Sclκ hold time after WR <sup>↑</sup>    |                  | 30     |             |       | 40     |             |       | ns    |

| tr       | Input rise time                         | ]                |        |             | 25    |        |             | 25    | ns    |

| tf       | Input fall time                         |                  |        |             | 25    |        |             | 25    | ns    |

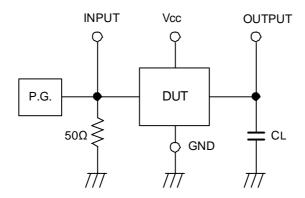

Note 1. Test Circuit

- (1) The pulse generator (PG) has the following characteristics. : tr=3ns, tf=3ns

- (2) The capacitance CL includes stray wiring capacitance and the probe input capacitance.

### **TIMING CHARTS**

Note 2. (1)Shaded portions indicate that switching is possible during those periods.

(2)PWM outputs 1 to 4 change synchronously with internal clock signals Φ.

The frequency of these signals is the 1/2 divider of the frequency input from XIN.

# APPLICATION EXAMPLE (Combination with electronic control for amplifier system)

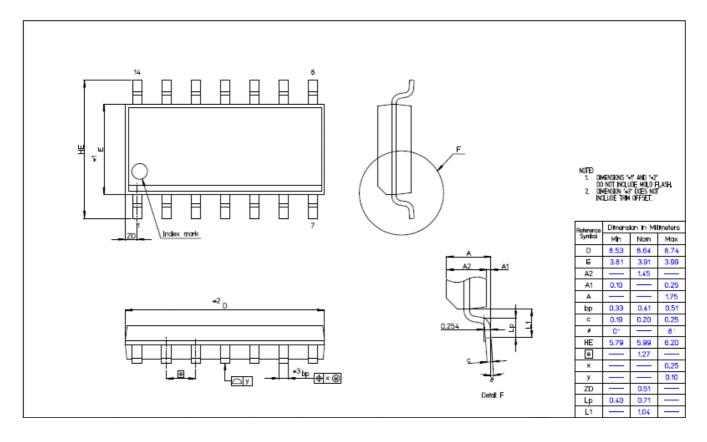

# PACKAGE OUTLINE

| Package   | RENESAS Code | Previous Code |

|-----------|--------------|---------------|

| 14pin SOP | PRSP0014DG-A | 14P2X-B       |

All trademarks and registered trademarks are the property of their respective owners.

### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- tes:

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- Tou should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products of technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document, but Renesas assumes in light of the total system before deciding about the applicability of such information to the infended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as astely systems, or equipment or systems for transportation and traffic, heldere, combustion control, aerospace and aeronau

http://www.renesas.com

#### RENESAS SALES OFFICES

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510