# NT68F632

### 8-Bit Microcontroller for LCD Monitor (128K Flash Memory Type)

# **Section-1 General Description**

#### 1-1 Features

- CMOS technology for low power consumption

- Operating voltage Vcc ranges from 3.0V to 3.6V

- 8031 8-bit CMOS Micro-Processor (uP) core

- Intel compatible 8031 architecture

- 256-byte Internal DATA Memory

- Two 16-Bit Timer/Counter

- Fully duplex UART

- 5-vector interrupt structure with two programmable priority levels

- High level C-language for the F/W development

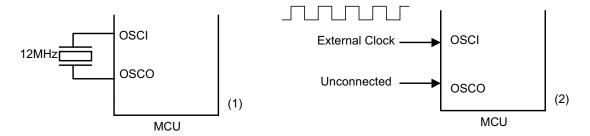

- On-Chip Oscillator → 12MHz operating frequency

- 24MHz clock for CPU operating

- Reset

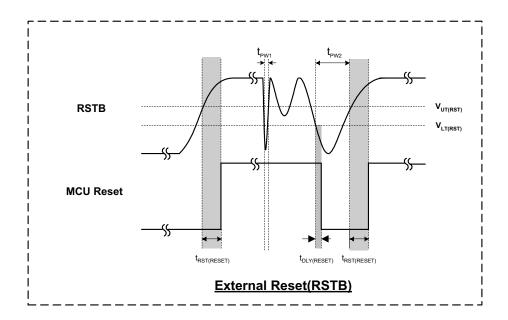

- External Reset Pin

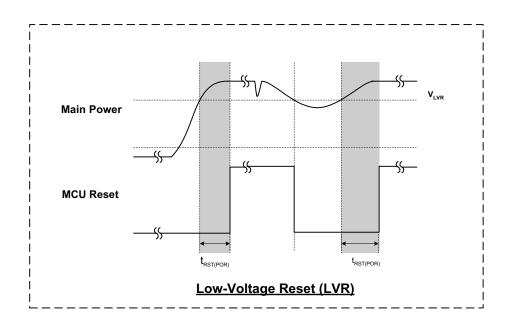

- Low-Voltage Reset

- Watch-Dog Timer Reset

- ISP Reset

- Program memory

- 128K bytes of on-chip flash memory for program memory

- 2K bytes of Mask ROM for ISP control function

- 1,536 Bytes On-Chip RAM

- Extended 256 Bytes Internal DATA Memory of uP 8031

- External Data Memory

- 768 Bytes General Purpose RAM Buffer (\$F400 ~ \$F6FF)

- 512 Bytes RAM Buffer for hardware DDC Port (\$F800 ~ \$F9FF)

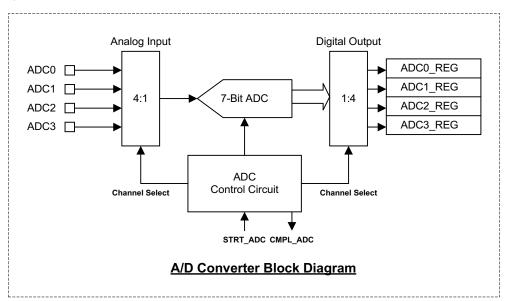

- A/D Converter

- 7-Bit resolution

- 4 selectable Input channels

- Conversion Range ➤ Absolutely Monotonic linear from GND to VCC

- Conversion time

12us

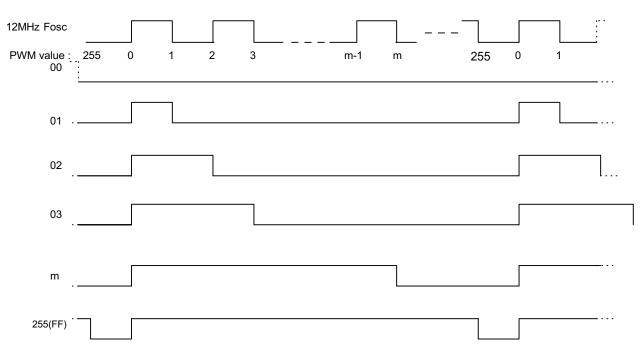

- PWM D/A Converter

- 8-Bit resolution

- 10 selectable output channels

- 6 channels with 3.3V Push-Pull Structure

- 4 channels with 5V Open-Drain Structure

- 35 (37 for PLCC Package) Selectable General Purpose I/O Pins

- Interrupts ⇒ 5-vector interrupt structure with two programmable priority levels for uP F8031

- TF0: Timer/Counter 0 Overflow Interrupt

- TF1: Timer/Counter 1 Overflow Interrupt

- RI+TI: UART Interrupts

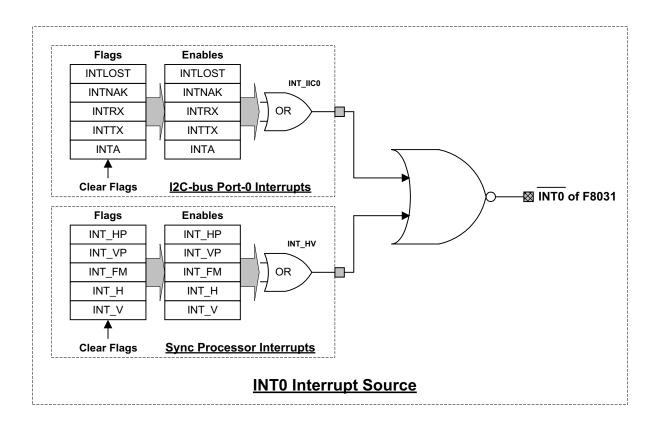

- INT0:

- Sync Processor Interrupts

- I2C Bus Port-0 (PB4, PB5) Interrupt

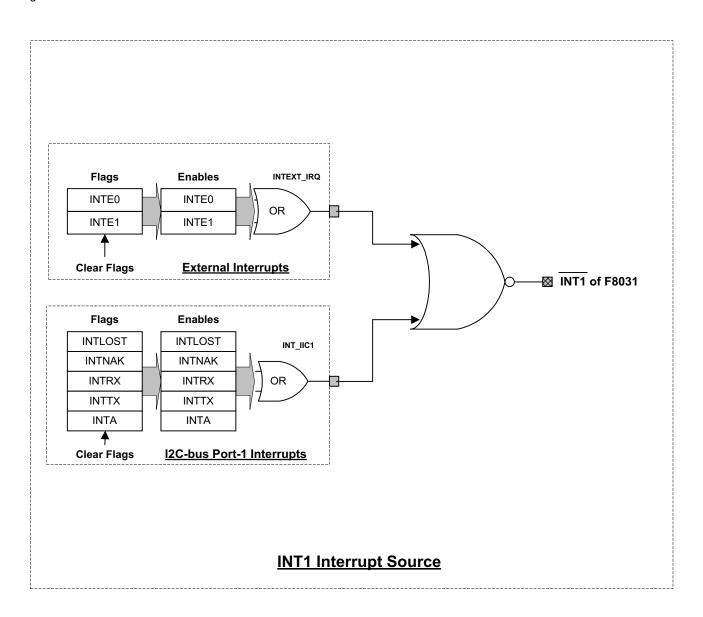

- INT1

- External Interrupts: INTE0 & INTE1

- I<sup>2</sup>C-Bus Port-1 (PB6, PB7) Interrupts

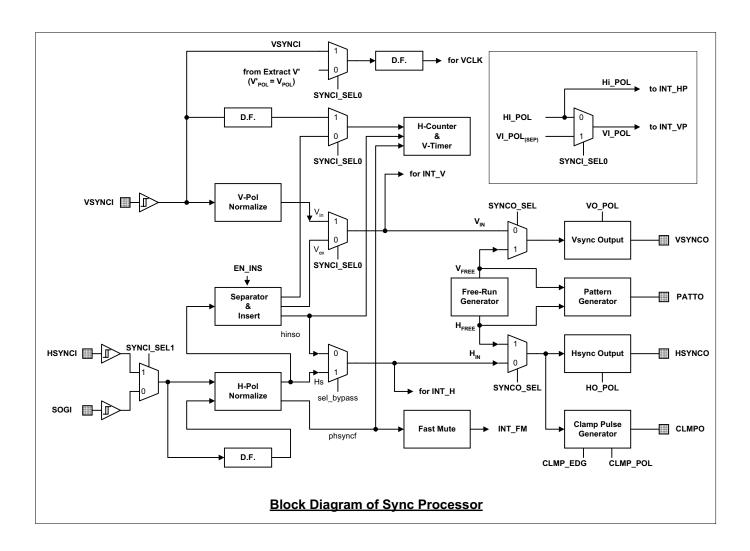

- Sync Processor Unit

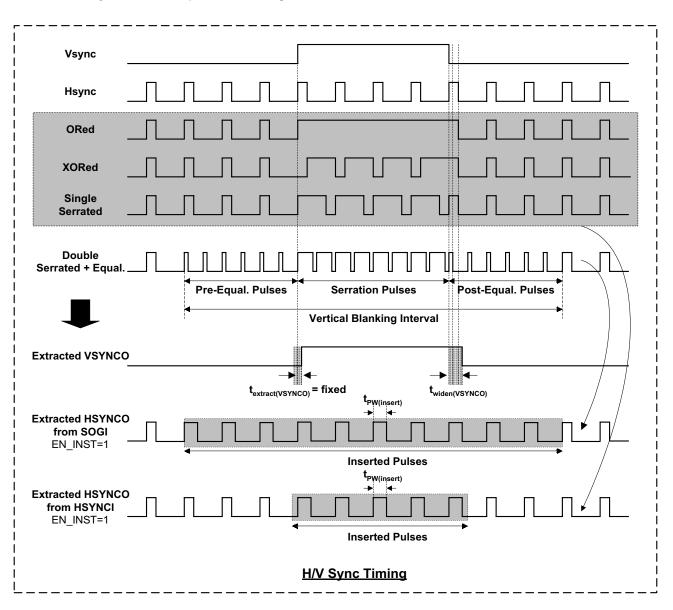

- Signal Type ➤ Separate Sync, Composite Sync & Digital-Level Sync-On-Green (SOG)

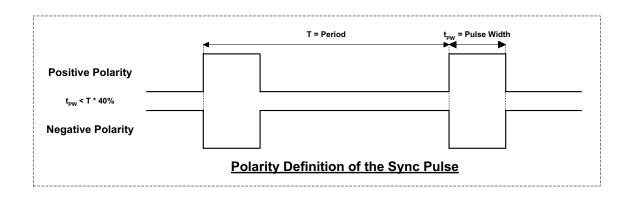

- Powerful Polarity detection for HSYNCI and VSYNCI

- HSYNCO/VSYNCO polarity-controlled outputs

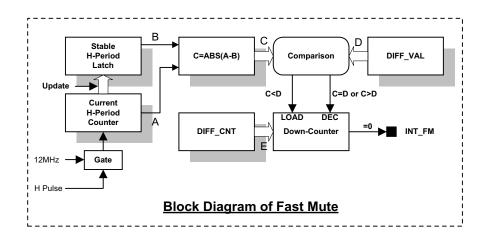

- Fast Auto-Mute function

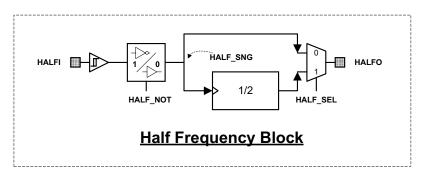

- Half frequency I/O function

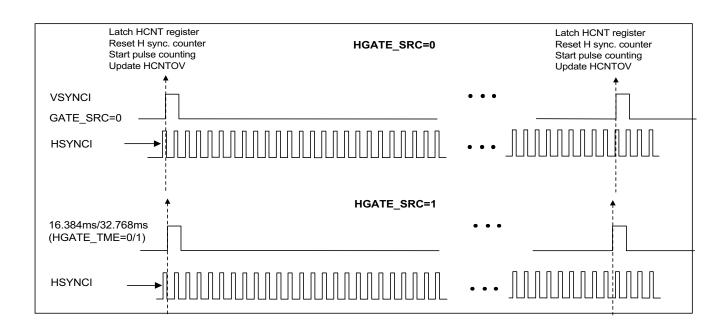

- Timer/Counters with 2-lay content latches for counting sync period/frequency → stable results can be read

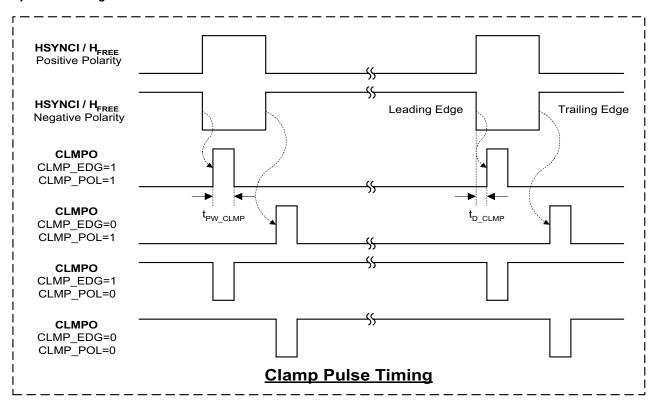

- Clamp pulse output

- Clamp pulse output at either the leading edge or trailing edge of HSYNC

- Selectable Clamp pulse width

- Selectable pulse output polarity

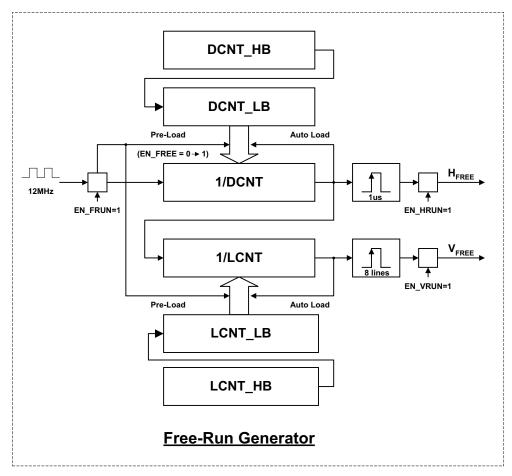

- Flexible free-run H/V sync output generator

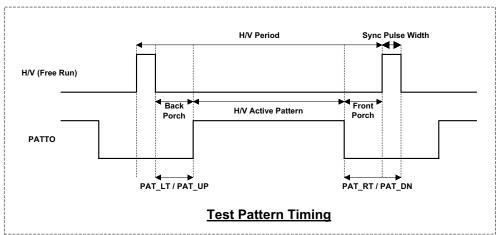

- Flexible test pattern generator

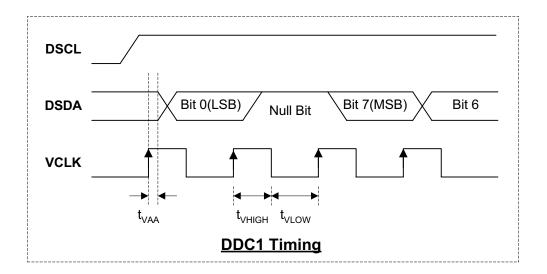

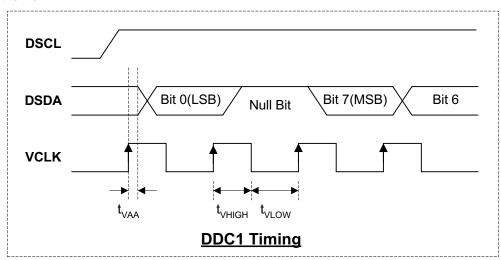

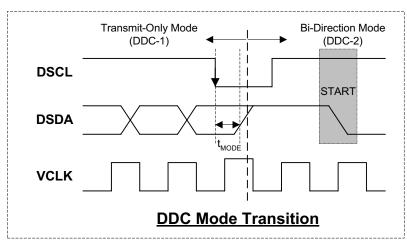

#### ■ DDC Port

- Dual indepentent input DDC channels

- Pure hardware solution for VESA DDC1/2B

- Selectable 128/256 Bytes EDID-Buffer for hardware DDC port

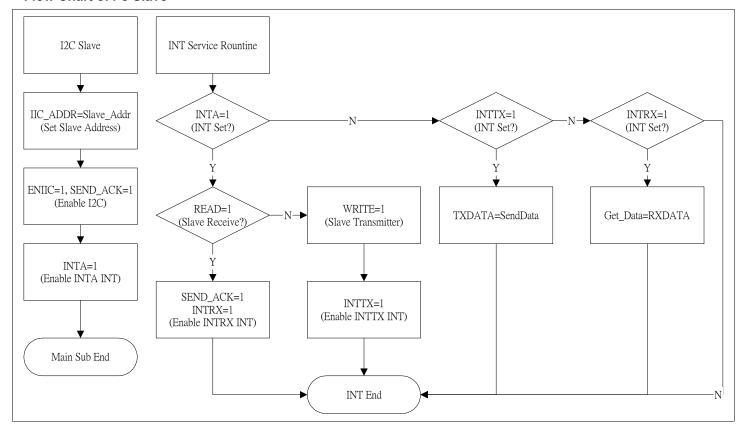

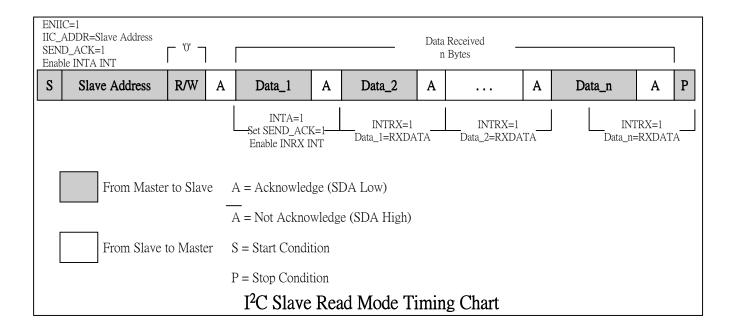

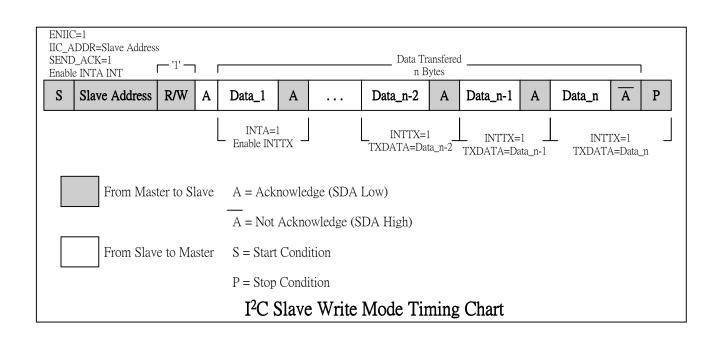

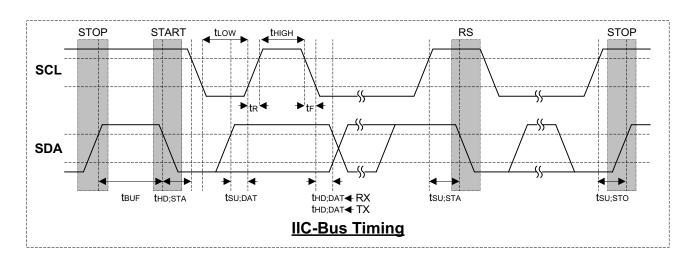

#### ■ I<sup>2</sup>C-bus

- Two built-in master/slave I<sup>2</sup>C bus interfaces support VESA 2Bi/2B+

- SCL clock speed supports up to 400Kbps

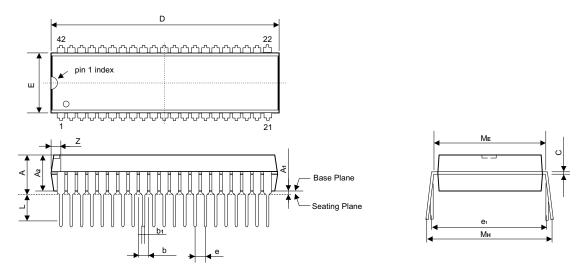

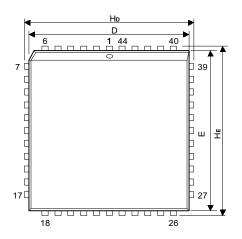

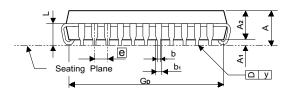

#### ■ Package

- 42-Pin S-DIP

- 44-Pin PLCC

#### 1-2 General Description

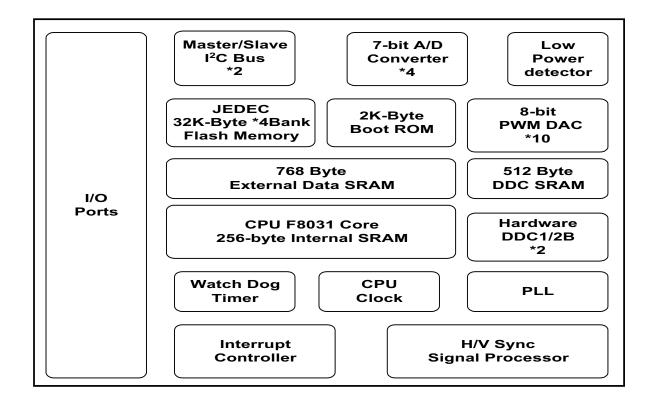

This is an 8031 CPU core embedded micro-controller, which is designed for the high-performance low-cost LCD monitor control application. It contains an 8-bit 8031 micro-controller, on-chip 128K bytes flash-type program ROM, 1,536-bytes internal data memory, four 7-bit resolution A/D Converter, 10-channel 8-bit resolution PWM DAC, two16-bit timer/counters, and an UART. Besides those, it has an internal SYNC processor, two-channel hardware DDC solution, and VESA 2Bi/2B+ master/slave I<sup>2</sup>C bus interface. Those functions can help the user to develop a LCD monitor application as soon as possible.

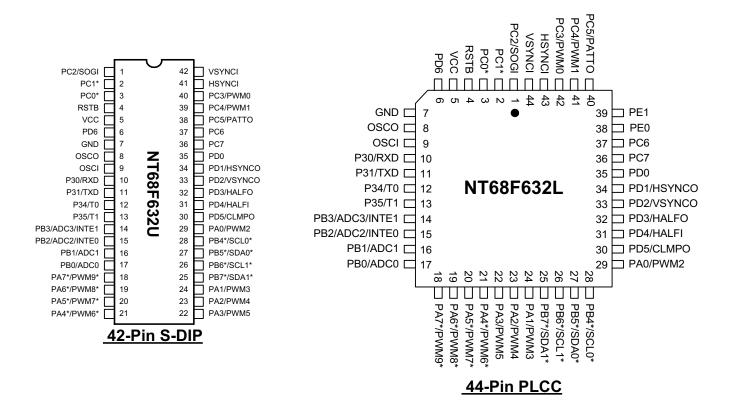

### 1-3 Pin Configurations

Note: The "\* " represents the 5V open-drain structures.

### 1-4 Block Diagram

# 1-5 Pin Descriptions

| Pin    | No.        | Desimation     | Fatian   |     | Description                                                        |

|--------|------------|----------------|----------|-----|--------------------------------------------------------------------|

| 44-Pin | 42-Pin     | Designation    | Function | I/O | Description                                                        |

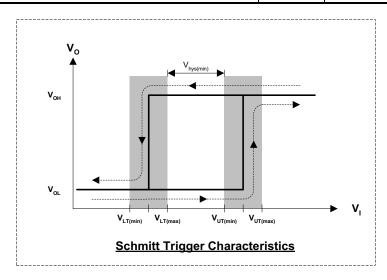

|        |            |                | PC2      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 1      | 1          | PC2/SOGI       | SOGI     | I   | Digital-Level Sync-On-Green Sync Input; with Schmitt Trigger Input |

| 2      | 2          | PC1*           | PC1*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input        |

| 3      | 3          | PC0*           | PC0*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input        |

| 4      | 4          | RSTB           | RSTB     | I   | Active-Low Reset Input; with Schmitt Triger Input                  |

| 5      | 5          | VCC            | VCC      | PWR | +3.3V Power Supply Input                                           |

| 6      | 6          | PD6            | PD6      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 7      | 7          | GND            | GND      | PWR | Power Ground                                                       |

| 8      | 8          | osco           | osco     | 0   | 12MHz External Crystal OSC Output                                  |

| 9      | 9          | OSCI           | OSCI     | I   | 12MHz External Crystal OSC Input                                   |

| 10     | 10         | D20/DVD        | P30      | I/O | GPIO Port-30 of Micro-Processor F8031                              |

| 10     | 10 P30/RXD |                | RXD      | I   | UART RX Data Input of Micro-Processor F8031                        |

| 11     | 11         | P31/TXD        | P31      | I/O | GPIO Port-31 of Micro-Processor F8031                              |

| 11     | 11         |                | TXD      | 0   | UART TX Data Output of Micro-Processor F8031                       |

| 12     | 12         | P34/T0         | P34      | I/O | GPIO Port-34 of Micro-Processor F8031                              |

| 12     | 12         | P34/10         | T0       | I   | Counter/Timer T0 Input of Micro-Processor F8031                    |

| 13     | 13         | D25/T1         | P35      | I/O | GPIO Port-35 of Micro-Processor F8031                              |

| 13     | 13         | P35/T1         | T1       | I   | Counter/Timer T1 Input of Micro-Processor F8031                    |

|        |            |                | PB3      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 14     | 14         | PB3/ADC3/INTE1 | ADC3     | I   | A/D Converter Input-3; Hi-Z input                                  |

|        |            |                | INTE1    | I   | External Interrupt input 1; Schmitt Trigger Input                  |

|        |            |                | PB2      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 15     | 15         | PB2/ADC2/INTE0 | ADC2     | I   | A/D Converter Input-2; Hi-Z input                                  |

|        |            |                | INTE0    | I   | External Interrupt input 0, Schmitt Trigger Input                  |

| 16     | 16         | DD4/ADC4       | PB1      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 16     | 16         | PB1/ADC1       | ADC1     | I   | A/D Converter Input-1; Hi-Z input                                  |

| 17     | 17         | DD0/4D00       | PB0      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input            |

| 17     | 17         | PB0/ADC0       | ADC0     | I   | A/D Converter Input-0; Hi-Z input                                  |

# Pin Descriptions (Continued)

| Pin    | No.    | Desimotion              | Function | 1/0 | Description                                                                                            |

|--------|--------|-------------------------|----------|-----|--------------------------------------------------------------------------------------------------------|

| 44-Pin | 42-Pin | Designation             | Function | I/O | Description                                                                                            |

| 18     | 18     | D A 7*/D\\/\\\0*        | PA7*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input                                            |

| 10     | 10     | PA7*/PWM9*              | PWM9*    | 0   | PWM-Type D/A Converter; 5V Open-Drain Structure                                                        |

| 19     | 19     | PA6*/PWM8*              | PA6*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input                                            |

| 19     | 19     | PAO /PVVIVIO            | PWM8*    | 0   | PWM-Type D/A Converter; 5V Open-Drain Structure                                                        |

| 20     | 20     | PA5*/PWM7*              | PA5*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input                                            |

| 20     | 20     | FAS /FWWI               | PWM7*    | 0   | PWM-Type D/A Converter; 5V Open-Drain Structure                                                        |

| 21     | 21     | PA4*/PWM6*              | PA4*     | I/O | I/O Pin; 5V Open-Drain Structure with Schmitt Trigger Input                                            |

| 21     | 21     | FA4 /FWINIO             | PWM6*    | 0   | PWM-Type D/A Converter; 5V Open-Drain Structure                                                        |

| 22     | 22     | PA3/PWM5                | PA3      | I/O | I/O Pin; Schmitt Trigger Input                                                                         |

| 22     | 22     | FA3/FWW3                | PWM5     | 0   | PWM-Type D/A Converter; 3.3V Push-Pull Structure                                                       |

| 23     | 23     | PA2/PWM4                | PA2      | I/O | I/O Pin; Schmitt Trigger Input                                                                         |

| 23     | 23     | FA2/FVVIVI4             | PWM4     | 0   | PWM-Type D/A Converter; 3.3V Push-Pull Structure                                                       |

| 24     | 24     | D A 4 /D\A/A 40         | PA1      | I/O | I/O Pin; Schmitt Trigger Input                                                                         |

| 24     | 24     | PA1/PWM3                | PWM3     | 0   | PWM-Type D/A Converter; 3.3V Push-Pull Structure                                                       |

|        |        |                         | PB7*     | I/O | I/O Pin; Open-Drain with Schmitt Trigger Input                                                         |

| 25     | 25     | PB7*/SDA1*              | SDA1*    | I/O | 5V Open-Drain Serial Data I/O Pin for the DDC Port 1 and the slave/master I <sup>2</sup> C-Bus Port 1  |

|        |        |                         | PB6*     | I/O | 5V I/O Pin; Open-Drain with Schmitt Trigger Input                                                      |

| 26     | 26     | PB6*/SCL1*              | SCL1*    | I/O | 5V Open-Drain Serial Clock I/O Pin for the DDC Port 1 and the slave/master I <sup>2</sup> C-Bus Port 1 |

|        |        |                         | PB5*     | I/O | 5V I/O Pin; Open-Drain with Schmitt Trigger Input                                                      |

| 27     | 27     | PB5*/SDA0*              | SDA0*    | 1/0 | 5V Open-Drain Serial Data I/O Pin for the DDC Port 0 and the slave/master I <sup>2</sup> C-Bus Port 0  |

|        |        |                         | PB4*     | I/O | 5V I/O Pin; Open-Drain with Schmitt Trigger Input                                                      |

| 28     | 28     | PB4*/SCL0*              | SCL0*    | I/O | 5V Open-Drain Serial Clock I/O Pin for the DDC Port 0 and the slave/master I <sup>2</sup> C-Bus Port 0 |

| 20     | 20     | D A O / D \ A \ A \ A \ | PA0      | I/O | I/O Pin; Schmitt Trigger Input                                                                         |

| 29     | 29     | PA0/PWM2                | PWM2     | 0   | PWM-Type D/A Converter; 3.3V Push-Pull Structure                                                       |

|        |        |                         | PD5      | I/O | I/O Pin; Push-Pull Structure with Schmitt Trigger Input                                                |

| 30     | 30     | PD5/CLMPO               | CLMPO    | 0   | Clamp Pulse Output for DC restoration of the Video Signal; Push-Pull Structure                         |

# Pin Descriptions (Continued)

| Pin    | No.    | Danissa etias | F4:      |      | D                                                          |

|--------|--------|---------------|----------|------|------------------------------------------------------------|

| 44-Pin | 42-Pin | Designation   | Function | I/O  | Description                                                |

| 31     | 31     | PD4/HALFI     | PD4      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 51     | 31     | FD4/HALFI     | HALFI    | I    | Half Frequency Input; Schmitt Trigger Input                |

| 00     | 20     | DD0/IIAI FO   | PD3      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 32     | 32     | PD3/HALFO     | HALFO    | 0    | Half Frequency Output; Push-Pull Structure                 |

| 22     | 22     | DD24/CVNCO    | PD2      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 33     | 33     | PD2/VSYNCO    | VSYNCO   | 0    | Vertical Sync Output; Push-Pull Structure                  |

| 0.4    | 24     | DD4/I-IOVALGG | PD1      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 34     | 34     | PD1/HSYNCO    | HSYNCO   | 0    | Horizontal Sync Output; Push-Pull Structure                |

| 35     | 35     | PD0           | PD0      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 36     | 36     | PC7           | PC7      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 37     | 37     | PC6           | PC6      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 0.0    |        | D05/D4TT0     | PC5      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 38     | 38     | PC5/PATTO     | PATTO    | 0    | Test Pattern Output; Push-Pull Structure                   |

| 20     | 20     | DO4/DWA44     | PC4      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 39     | 39     | PC4/PWM1      | PWM1     | 0    | PWM-Type D/A Converter; Push-Pull Structure                |

| 40     | 40     | DC2/DWM0      | PC3      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

| 40     | 40     | PC3/PWM0      | PWM0     | 0    | PWM-Type D/A Converter; Push-Pull Structure                |

| 41     | _      | PE0           | PE0      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

|        |        | . 20          | . 20     | .,,  | Only available in 44-Pin PLCC                              |

| 42     | -      | PE1           | PE1      | I/O  | I/O Pin; Push-Pull Structure with Schmitt Trigger Input    |

|        |        |               |          | ., 0 | Only available in 44-Pin PLCC                              |

| 43     | 41     | HSYNCI        | HSYNCI   | I    | Horizontal and Composite sync Input; Schmitt Trigger Input |

| 44     | 42     | VSYNCI        | VSYNCI   | I    | VSYNC/Interrupt Input; Schmitt Trigger Input               |

Note: The " "\* " represents the open-drain structures.

# **Section-2 Memory Allocation**

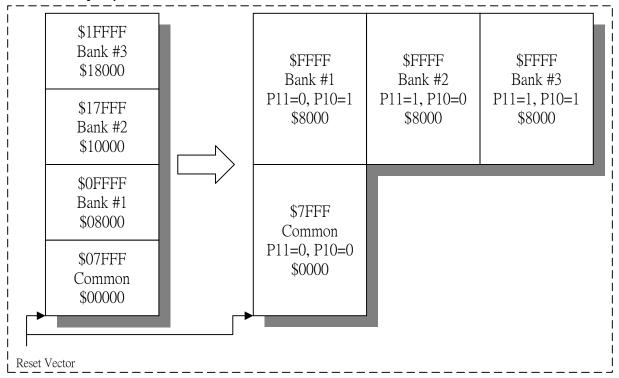

The standard uP F8031 can support up to 64K-byte external Program Memory size and 64K-byte external DATA Memory size. Now we expand the program memory up to 128K bytes by using the bank switching technique. And we have external 1,536 bytes of data memory for software development. They are described as follows:

### 2-1 Program Memory

- 128K Bytes on-chip flash memory for user code.

- 2K Bytes mask-type Boot ROM for ISP function.

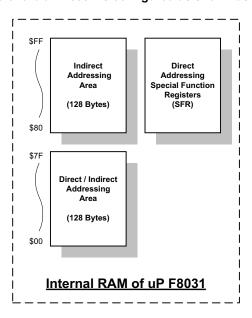

#### 2-2 Data Memory

- Internal RAM: There are totally **256 bytes** internal DATA Memory of the uP F8031.

- Internal Special Function Registers (SFR): There are 128 bytes SFR, which is the internal reserved memory for system registers of the uP F8031.

- External DATA Memory

- **768** Bytes general purpose RAM buffer, address maping from \$F400H to \$F6FFH.

- 512 Bytes external data memory reserved for EDID buffer of the Hardware DDC Port, range from \$F800H to \$F9FFH

### 2-3 Interrupt Vectors

| Address | Interrupt Source | Description                                                 |

|---------|------------------|-------------------------------------------------------------|

| 0000H   | Reset            | System Reset                                                |

| 0003H   | IE0              | External INT0 Interrupt of the uP F8031                     |

| 000BH   | TF0              | Timer/Cunter 0 Overflow Interrupt of the uP F8031           |

| 0013H   | IE1              | External INT1 Interrupt the of uP F8031                     |

| 001BH   | TF1              | Timer/Cunter 1 Overflow Interrupt of the uP F8031           |

| 0023H   | RI & TI          | UART Transmit interrupt & Receive interrupt of the uP F8031 |

### 2-4 Memory Map

- The Internal Data Memory Map of the uP F8031 is configured as shown as below

#### - The External Memory Map in Normal Mode

External Memory Map of the uP F8031 in Normal Mode

2-5 System Registers

|        | ystem Regi                                        | 01010  |     |          | General I/O | Ports Cont   | rol Registers | 6       |         |         |         |

|--------|---------------------------------------------------|--------|-----|----------|-------------|--------------|---------------|---------|---------|---------|---------|

| Addr.  | Name                                              | Init.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

| \$F000 | PortA                                             | \$0FH  | R/W | PA7      | PA6         | PA5          | PA4           | PA3     | PA2     | PA1     | PA0     |

| \$F001 | PortB                                             | \$FFH  | R/W | PB7      | PB6         | PB5          | PB4           | PB3     | PB2     | PB1     | PB0     |

| \$F002 | PortC                                             | \$FCH  | R/W | PC7      | PC6         | PC5          | PC4           | PC3     | PC2     | PC1     | PC0     |

| \$F003 | PortD                                             | \$7FH  | R/W | -        | PD6         | PD5          | PD4           | PD3     | PD2     | PD1     | PD0     |

| \$F004 | PortE                                             | \$03H  | R/W | -        | -           | -            | -             | -       | -       | PE1     | PE0     |

|        | General I/O Ports R/W Direction Control Registers |        |     |          |             |              |               |         |         |         |         |

| Addr.  | Name                                              | lnit.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

| \$F005 | RDPA_REG                                          | \$0FH  | R/W | RDPA_7   | RDPA_6      | RDPA_5       | RDPA_4        | RDPA_3  | RDPA_2  | RDPA_1  | RDPA_0  |

| \$F006 | RDPB_REG                                          | \$FFH  | R/W | RDPB_7   | RDPB_6      | RDPB_5       | RDPB_4        | RDPB_3  | RDPB_2  | RDPB_1  | RDPB_0  |

| \$F007 | RDPC_REG                                          | \$FCH  | R/W | RDPC_7   | RDPC_6      | RDPC_5       | RDPC_4        | RDPC_3  | RDPC_2  | RDPC_1  | RDPC_0  |

| \$F008 | RDPD_REG                                          | \$7FH  | R/W | -        | RDPD_6      | RDPD_5       | RDPD_4        | RDPD_3  | RDPD_2  | RDPD_1  | RDPD_0  |

| \$F009 | RDPE_REG                                          | \$03H  | R/W | -        | -           | -            | -             | -       | -       | RDPE_1  | RDPE_0  |

|        |                                                   |        |     |          | Watch-Dog   | Timer Con    | trol Register | •       |         |         |         |

| Addr.  | Name                                              | lnit.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

| \$F00A | CLRWDT                                            | \$55H  | W   | 0        | 1           | 0            | 1             | 0       | 1       | 0       | 1       |

|        |                                                   |        | -   |          | A/D Conv    | erter Contro | l Registers   |         |         |         |         |

| Addr.  | Name                                              | lnit.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

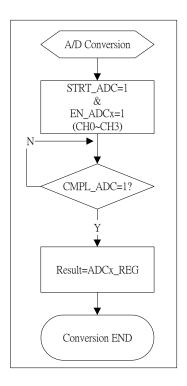

| ФE00D  | ADC CON                                           | ФООL I | W   | STRT_ADC | -           | -            | -             | EN_ADC3 | EN_ADC2 | EN_ADC1 | EN_ADC0 |

| \$F00B | ADC_CON                                           | \$00H  | R   | -        | -           | -            | -             | EN_ADC3 | EN_ADC2 | EN_ADC1 | EN_ADC0 |

| \$F00C | ADC0                                              | \$00H  | R   | -        | AD06        | AD05         | AD04          | AD03    | AD02    | AD01    | AD00    |

| \$F00D | ADC1                                              | \$00H  | R   | -        | AD16        | AD15         | AD14          | AD13    | AD12    | AD11    | AD10    |

| \$F00E | ADC2                                              | \$00H  | R   | -        | AD26        | AD25         | AD24          | AD23    | AD22    | AD21    | AD20    |

| \$F00F | ADC3                                              | \$00H  | R   | CMP_ADC  | AD36        | AD35         | AD34          | AD33    | AD32    | AD31    | AD30    |

|        |                                                   |        |     | P        | WM Channe   | l Enable Co  | ntrol Regist  | ers     | -       |         | -       |

| Addr.  | Name                                              | lnit.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

| \$F010 | ENPWM_LB                                          | \$00H  | R/W | -        | -           | -            | -             | -       | -       | EN_PWM1 | EN_PWM0 |

| \$F011 | ENPWM_HB                                          | \$00H  | R/W | EN_PWM9  | EN_PWM8     | EN_PWM7      | EN_PWM6       | EN_PWM5 | EN_PWM4 | EN_PWM3 | EN_PWM2 |

|        |                                                   |        |     |          | PWM Chanr   | nel 0~9 Cont | rol Register  | s       |         |         |         |

| Addr.  | Name                                              | lnit.  | R/W | Bit7     | Bit6        | Bit5         | Bit4          | Bit3    | Bit2    | Bit1    | Bit0    |

| \$F012 | PWM0                                              | \$80H  | R/W | PWM07    | PWM06       | PWM05        | PWM04         | PWM03   | PWM02   | PWM01   | PWM00   |

| \$F013 | PWM1                                              | \$80H  | R/W | PWM17    | PWM16       | PWM15        | PWM14         | PWM13   | PWM12   | PWM11   | PWM10   |

| \$F014 | PWM2                                              | \$80H  | R/W | PWM27    | PWM26       | PWM25        | PWM24         | PWM23   | PWM22   | PWM21   | PWM20   |

| \$F015 | PWM3                                              | \$80H  | R/W | PWM37    | PWM36       | PWM35        | PWM34         | PWM33   | PWM32   | PWM31   | PWM30   |

| \$F016 | PWM4                                              | \$80H  | R/W | PWM47    | PWM46       | PWM45        | PWM44         | PWM43   | PWM42   | PWM41   | PWM40   |

| \$F017 | PWM5                                              | \$80H  | R/W | PWM57    | PWM56       | PWM55        | PWM54         | PWM53   | PWM52   | PWM51   | PWM50   |

| \$F018 | PWM6                                              | \$80H  | R/W | PWM67    | PWM66       | PWM65        | PWM64         | PWM63   | PWM62   | PWM61   | PWM60   |

| \$F019 | PWM7                                              | \$80H  | R/W | PWM77    | PWM76       | PWM75        | PWM74         | PWM73   | PWM72   | PWM71   | PWM70   |

| \$F01A | PWM8                                              | \$80H  | R/W | PWM87    | PWM86       | PWM85        | PWM84         | PWM83   | PWM82   | PWM81   | PWM80   |

| \$F01B | PWM9                                              | \$80H  | R/W | PWM97    | PWM96       | PWM95        | PWM94         | PWM93   | PWM92   | PWM91   | PWM90   |

# System Registers (Continued)

|                                                                                                                                                                        | ii Registers                                                                                                                                     | `                                                                                                                                      |                                                                                         |                                                                                                            | are DDC Por                                                                                         | t-0 Control                                                                                   | Registers (P                                                                             | B4 PB5)                                                                                                                     |                                                                                                                                  |                                                                                                                    |                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | Init.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

| Addi.                                                                                                                                                                  | Name                                                                                                                                             | \$48H                                                                                                                                  | R                                                                                       | EN DDC                                                                                                     | WPT DDC                                                                                             | LEN_EDID                                                                                      | MODE                                                                                     | EN BACK                                                                                                                     | INTV CLK                                                                                                                         | Diti                                                                                                               | UPD DDC                                                                                                        |

| \$F01C                                                                                                                                                                 | DDC_CTL0                                                                                                                                         | φ <del>4</del> 011                                                                                                                     | W                                                                                       | EN DDC                                                                                                     | WPT_DDC                                                                                             | LEN EDID                                                                                      | MODE                                                                                     | EN BACK                                                                                                                     | INTV_CLK                                                                                                                         | CLR PTR                                                                                                            | CLR_UPD                                                                                                        |

| \$F01D                                                                                                                                                                 | DDC ADDR0                                                                                                                                        | \$00H                                                                                                                                  | W                                                                                       | VALID_3                                                                                                    | VALID 2                                                                                             | VALID_1                                                                                       | WODL                                                                                     | ADDR 3                                                                                                                      | ADDR_2                                                                                                                           | ADDR_1                                                                                                             | CLK_OFD                                                                                                        |

| \$1010                                                                                                                                                                 | DDC_ADDR0                                                                                                                                        | φυσιι                                                                                                                                  | VV                                                                                      |                                                                                                            |                                                                                                     |                                                                                               | Danistana (D                                                                             |                                                                                                                             | ADDR_Z                                                                                                                           | ADDK_1                                                                                                             | -                                                                                                              |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         |                                                                                                            | are DDC Por                                                                                         |                                                                                               | <u> </u>                                                                                 |                                                                                                                             |                                                                                                                                  |                                                                                                                    |                                                                                                                |

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | Init.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

| \$F01E                                                                                                                                                                 | DDC_CTL1                                                                                                                                         | \$48H                                                                                                                                  | R                                                                                       | EN_DDC                                                                                                     | WPT_DDC                                                                                             | LEN_EDID                                                                                      | MODE                                                                                     | EN_BACK                                                                                                                     | INTV_CLK                                                                                                                         | -                                                                                                                  | UPD_DDC                                                                                                        |

|                                                                                                                                                                        |                                                                                                                                                  | -                                                                                                                                      | W                                                                                       | EN_DDC                                                                                                     | WPT_DDC                                                                                             | LEN_EDID                                                                                      | MODE                                                                                     | EN_BACK                                                                                                                     | INTV_CLK                                                                                                                         | CLR_PTR                                                                                                            | CLR_UPD                                                                                                        |

| \$F01F                                                                                                                                                                 | DDC_ADDR1                                                                                                                                        | \$00H                                                                                                                                  | W                                                                                       | VALID_3                                                                                                    | VALID_2                                                                                             | VALID_1                                                                                       | -                                                                                        | ADDR_3                                                                                                                      | ADDR_2                                                                                                                           | ADDR_1                                                                                                             | -                                                                                                              |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         |                                                                                                            | Interrupt S                                                                                         | ource Contr                                                                                   | ol Registers                                                                             |                                                                                                                             |                                                                                                                                  |                                                                                                                    |                                                                                                                |

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | lnit.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

| \$F020                                                                                                                                                                 | INT_SRC                                                                                                                                          | \$00H                                                                                                                                  | R                                                                                       | -                                                                                                          | -                                                                                                   | INT_IIC0                                                                                      | INT_EXT                                                                                  | -                                                                                                                           | -                                                                                                                                | INT_IIC1                                                                                                           | INT_HV                                                                                                         |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         |                                                                                                            | <b>External Int</b>                                                                                 | errupt Cont                                                                                   | rol Register                                                                             | 5                                                                                                                           |                                                                                                                                  |                                                                                                                    |                                                                                                                |

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | lnit.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

| ФE024                                                                                                                                                                  | INTEXT_FLG                                                                                                                                       | \$00H                                                                                                                                  | R                                                                                       | -                                                                                                          | -                                                                                                   | -                                                                                             | -                                                                                        | -                                                                                                                           | -                                                                                                                                | INTE1                                                                                                              | INTE0                                                                                                          |

| \$F021                                                                                                                                                                 | INTEXT_CLR                                                                                                                                       | -                                                                                                                                      | W                                                                                       | ı                                                                                                          | -                                                                                                   | 1                                                                                             | -                                                                                        | 1                                                                                                                           | -                                                                                                                                | CLR_INTE1                                                                                                          | CLR_INTE0                                                                                                      |

| \$F022                                                                                                                                                                 | INTEXT_EN                                                                                                                                        | \$00H                                                                                                                                  | W                                                                                       | ı                                                                                                          | 1                                                                                                   | INTE1_EDG                                                                                     | INTE0_EDG                                                                                | ı                                                                                                                           | -                                                                                                                                | INTE1                                                                                                              | INTE0                                                                                                          |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         | Syr                                                                                                        | nc Processo                                                                                         | r Interrupt C                                                                                 | ontrol Regi                                                                              | sters                                                                                                                       |                                                                                                                                  |                                                                                                                    |                                                                                                                |

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | Init.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

| <b>Ф</b> Е000                                                                                                                                                          | INTHV_FLG                                                                                                                                        | \$00H                                                                                                                                  | R                                                                                       | INT_H                                                                                                      | INT_V                                                                                               | -                                                                                             | -                                                                                        | -                                                                                                                           | INT_HP                                                                                                                           | INT_VP                                                                                                             | INT_FM                                                                                                         |

| \$F023                                                                                                                                                                 | INTHV_CLR                                                                                                                                        | -                                                                                                                                      | W                                                                                       | INT_H                                                                                                      | INT_V                                                                                               | -                                                                                             | -                                                                                        | -                                                                                                                           | INT_HP                                                                                                                           | INT_VP                                                                                                             | INT_FM                                                                                                         |

| \$F024                                                                                                                                                                 | INTHV_EN                                                                                                                                         | \$00H                                                                                                                                  | R/W                                                                                     | INT_H                                                                                                      | INT_V                                                                                               | -                                                                                             | -                                                                                        | -                                                                                                                           | INT_HP                                                                                                                           | INT_VP                                                                                                             | INT_FM                                                                                                         |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         | Syr                                                                                                        | c Processo                                                                                          | r Interrupt C                                                                                 | ontrol Regis                                                                             | sters                                                                                                                       |                                                                                                                                  |                                                                                                                    |                                                                                                                |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         |                                                                                                            |                                                                                                     |                                                                                               |                                                                                          |                                                                                                                             | 7                                                                                                                                |                                                                                                                    |                                                                                                                |

| Addr.                                                                                                                                                                  | Name                                                                                                                                             | lnit.                                                                                                                                  | R/W                                                                                     | Bit7                                                                                                       | Bit6                                                                                                | Bit5                                                                                          | Bit4                                                                                     | Bit3                                                                                                                        | Bit2                                                                                                                             | Bit1                                                                                                               | Bit0                                                                                                           |

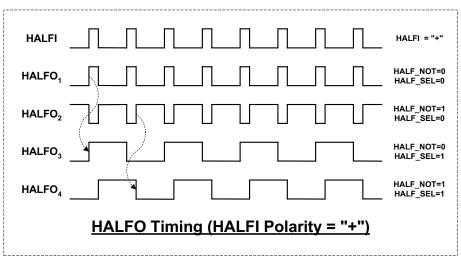

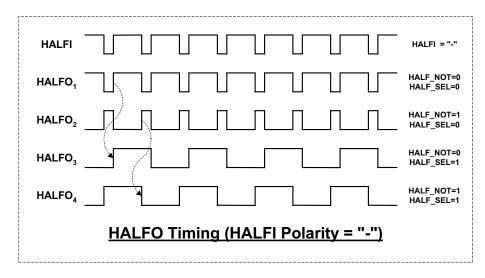

| Addr.<br>\$F025                                                                                                                                                        | Name<br>SYNC REG                                                                                                                                 | Init.<br>\$00H                                                                                                                         | R/W                                                                                     | Bit7<br>EN FRUN                                                                                            | Bit6<br>AUTO FLT                                                                                    | Bit5<br>EN SOG                                                                                | Bit4<br>EN CLMP                                                                          | Bit3<br>EN PAT                                                                                                              | Bit2<br>EN HALH                                                                                                                  | Bit1<br>HALF_SEL                                                                                                   | Bit0<br>HALF_NOT                                                                                               |

|                                                                                                                                                                        |                                                                                                                                                  |                                                                                                                                        |                                                                                         |                                                                                                            |                                                                                                     |                                                                                               |                                                                                          |                                                                                                                             |                                                                                                                                  |                                                                                                                    |                                                                                                                |

| \$F025<br>\$F026                                                                                                                                                       | SYNC_REG<br>HVO_REG                                                                                                                              | \$00H                                                                                                                                  | R/W                                                                                     | EN_FRUN                                                                                                    | AUTO_FLT                                                                                            | EN_SOG                                                                                        | EN_CLMP                                                                                  | EN_PAT                                                                                                                      | EN_HALH                                                                                                                          | HALF_SEL                                                                                                           | HALF_NOT                                                                                                       |

| \$F025                                                                                                                                                                 | SYNC_REG                                                                                                                                         | \$00H<br>\$00H                                                                                                                         | R/W<br>R/W                                                                              | EN_FRUN<br>EN_HOUT                                                                                         | AUTO_FLT<br>EN_VOUT                                                                                 | EN_SOG<br>EN_HRUN                                                                             | EN_CLMP                                                                                  | EN_PAT<br>EN_INS                                                                                                            | EN_HALH<br>SYNC_SEL                                                                                                              | HALF_SEL<br>HO_POL                                                                                                 | HALF_NOT<br>VO_POL                                                                                             |

| \$F025<br>\$F026                                                                                                                                                       | SYNC_REG<br>HVO_REG                                                                                                                              | \$00H<br>\$00H<br>\$E0H                                                                                                                | R/W<br>R/W<br>R                                                                         | EN_FRUN<br>EN_HOUT<br>SYNC_S1                                                                              | AUTO_FLT<br>EN_VOUT<br>SYNC_S0                                                                      | EN_SOG<br>EN_HRUN<br>INS_PW                                                                   | EN_CLMP                                                                                  | EN_PAT<br>EN_INS                                                                                                            | EN_HALH<br>SYNC_SEL                                                                                                              | HALF_SEL<br>HO_POL                                                                                                 | HALF_NOT<br>VO_POL                                                                                             |

| \$F025<br>\$F026<br>\$F027                                                                                                                                             | SYNC_REG<br>HVO_REG<br>HVI_REG                                                                                                                   | \$00H<br>\$00H<br>\$E0H                                                                                                                | R/W<br>R/W<br>R<br>W                                                                    | EN_FRUN<br>EN_HOUT<br>SYNC_S1<br>SYNC_S1                                                                   | AUTO_FLT<br>EN_VOUT<br>SYNC_S0<br>SYNC_S0                                                           | EN_SOG<br>EN_HRUN<br>INS_PW<br>INS_PW                                                         | EN_CLMP<br>EN_VRUN<br>-                                                                  | EN_PAT<br>EN_INS<br>H_LVL<br>-                                                                                              | EN_HALH<br>SYNC_SEL<br>V_LVL<br>-                                                                                                | HALF_SEL<br>HO_POL<br>H_POL<br>-                                                                                   | HALF_NOT<br>VO_POL<br>V_POL<br>-                                                                               |

| \$F025<br>\$F026<br>\$F027<br>\$F028                                                                                                                                   | SYNC_REG HVO_REG HVI_REG HPW_REG                                                                                                                 | \$00H<br>\$00H<br>\$E0H<br>-<br>\$00H                                                                                                  | R/W<br>R/W<br>R<br>W<br>R                                                               | EN_FRUN<br>EN_HOUT<br>SYNC_S1<br>SYNC_S1<br>HPW7                                                           | AUTO_FLT<br>EN_VOUT<br>SYNC_S0<br>SYNC_S0<br>HPW6                                                   | EN_SOG<br>EN_HRUN<br>INS_PW<br>INS_PW<br>HPW5                                                 | EN_CLMP EN_VRUN HPW4                                                                     | EN_PAT EN_INS H_LVL - HPW3                                                                                                  | EN_HALH SYNC_SEL V_LVL - HPW2                                                                                                    | HALF_SEL HO_POL H_POL - HPW1                                                                                       | HALF_NOT VO_POL V_POL - HPW0                                                                                   |

| \$F025<br>\$F026<br>\$F027<br>\$F028<br>\$F029                                                                                                                         | SYNC_REG<br>HVO_REG<br>HVI_REG<br>HPW_REG<br>HFLT_REG                                                                                            | \$00H<br>\$00H<br>\$E0H<br>-<br>\$00H<br>\$FFH                                                                                         | R/W<br>R/W<br>R<br>W<br>R<br>R/W                                                        | EN_FRUN<br>EN_HOUT<br>SYNC_S1<br>SYNC_S1<br>HPW7                                                           | AUTO_FLT<br>EN_VOUT<br>SYNC_S0<br>SYNC_S0<br>HPW6                                                   | EN_SOG<br>EN_HRUN<br>INS_PW<br>INS_PW<br>HPW5                                                 | EN_CLMP EN_VRUN HPW4                                                                     | EN_PAT EN_INS H_LVL - HPW3 HFLT3                                                                                            | EN_HALH SYNC_SEL V_LVL - HPW2 HFLT2                                                                                              | HALF_SEL HO_POL H_POL - HPW1 HFLT1                                                                                 | HALF_NOT VO_POL V_POL - HPW0 HFLT0                                                                             |

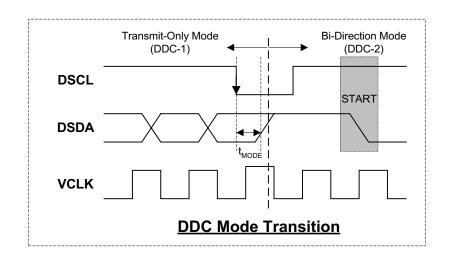

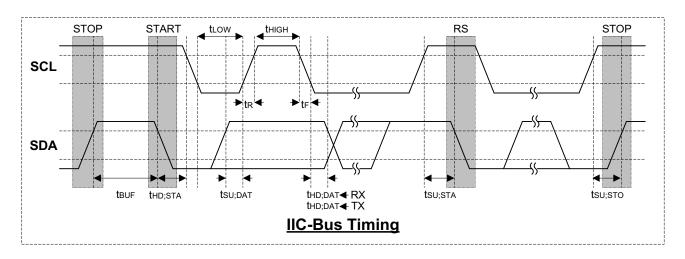

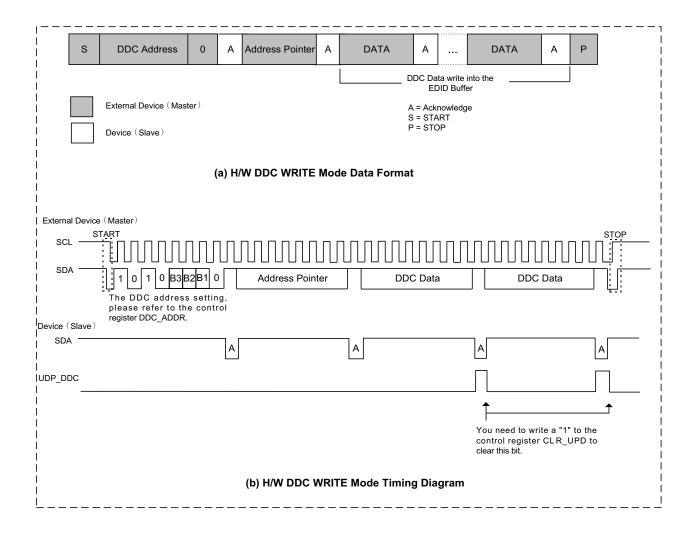

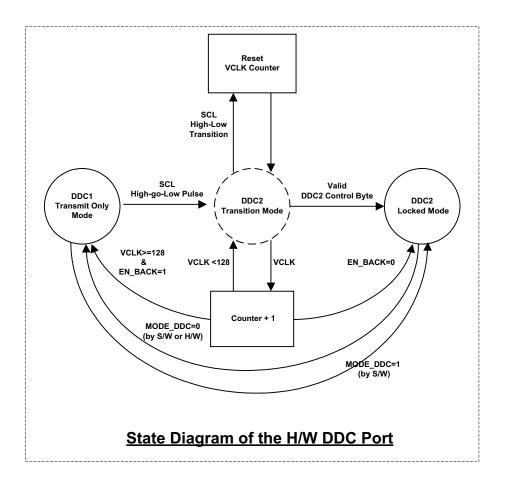

| \$F025<br>\$F026<br>\$F027<br>\$F028<br>\$F029<br>\$F02A                                                                                                               | SYNC_REG HVO_REG HVI_REG HPW_REG HFLT_REG CLMP_REG                                                                                               | \$00H<br>\$00H<br>\$E0H<br>-<br>\$00H<br>\$FFH<br>\$0CH                                                                                | R/W<br>R/W<br>R<br>W<br>R<br>R<br>W<br>W                                                | EN_FRUN<br>EN_HOUT<br>SYNC_S1<br>SYNC_S1<br>HPW7<br>HFLT7                                                  | AUTO_FLT<br>EN_VOUT<br>SYNC_S0<br>SYNC_S0<br>HPW6<br>HFLT6                                          | EN_SOG<br>EN_HRUN<br>INS_PW<br>INS_PW<br>HPW5<br>HFLT5                                        | EN_CLMP EN_VRUN HPW4 HFLT4 -                                                             | EN_PAT EN_INS H_LVL - HPW3 HFLT3 EDG                                                                                        | EN_HALH SYNC_SEL V_LVL - HPW2 HFLT2 POL                                                                                          | HALF_SEL HO_POL H_POL - HPW1 HFLT1 PW1 PAT_L1 PAT_R1                                                               | HALF_NOT<br>VO_POL<br>V_POL<br>-<br>HPW0<br>HFLT0<br>PW0                                                       |