### Hi3536C H.265 CODEC Processor

# **Brief Data Sheet**

lssue 01 Date 2017-02-28

#### Copyright © HiSilicon Technologies Co., Ltd. 2016-2017. All rights reserved.

No part of this document may be reproduced or transmitted in any form or by any means without prior written consent of HiSilicon Technologies Co., Ltd.

#### **Trademarks and Permissions**

(2), **HISILICON**, and other HiSilicon icons are trademarks of HiSilicon Technologies Co., Ltd. All other trademarks and trade names mentioned in this document are the property of their respective holders.

#### Notice

The purchased products, services and features are stipulated by the contract made between HiSilicon and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied.

The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

### HiSilicon Technologies Co., Ltd.

- Address: Huawei Industrial Base Bantian, Longgang Shenzhen 518129 People's Republic of China Website: http://www.hisilicon.com

- Email: support@hisilicon.com

### Hi3536C H.265 CODEC Processor

### **Key Specifications**

#### **Processor Core**

- ARM Cortex A7 dual-core

- Video Encoding/Decoding Protocols

- H.265/H.264/JPEG encoding and decoding

#### Video Encoding/Decoding

- 4x 1080p@30 fps H.265/H.264 decoding

- 8x 720p@30 fps H.265/H.264 decoding

- 16x D1@30 fps H.265/H.264 decoding

- 1x 1080p@ 30 fps H.265/H.264 encoding

#### Video and Graphics Processing

• Efficiently optimize and improve the image quality in various scenes by integrating HiSilicon 's most advanced image processing engine.

#### Audio Encoding/Decoding

- ADPCM, G.711, and G.726 hardware audio encoding

- Software audio encoding and decoding complying with multiple protocols

#### **Security Engine**

• AES, DES, and 3DES algorithms implemented by hardware

#### Video Interfaces

Support HDMI/VGA/CVBS output with high resolution up to 3840 x 2160

#### **Audio Interfaces**

• Support I<sup>2</sup>S/PCM interfaces

#### **Ethernet Ports**

• Two gigabit Ethernet ports

#### **Peripheral Interfaces**

• Support SATA 3.0 /USB 2.0 interfaces

#### **Memory Interfaces**

- DDR3 SDRAM

- Support SPI NOR/NAND flash

- Embedded 4 KB BOOTROM and 16 KB SRAM

#### **RTC with an Independent Power Supply**

• Independent battery for supplying power to the RTC

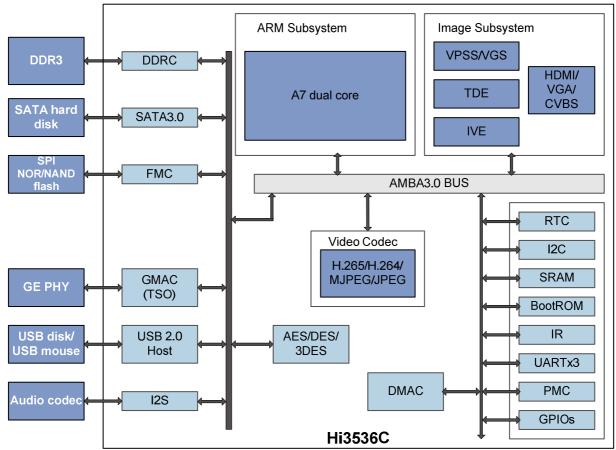

## **Functional Block Diagram**